Inihayag ng Synopsys na ang mga tool sa proseso ng disenyo nito at IP ay handa na para sa proseso ng pagmamanupaktura ng 2nm sa Samsung Wafer Foundry.Kamakailan lamang ay inihayag ng Samsung na ito ay makagawa ng masa na proseso ng 2NM na semiconductor chips noong 2025 at sinabi na ang proseso ay higit na mapabuti sa 2027. Ang tool ng disenyo ng EDA ng Synopsys ay pumasa sa sertipikasyon ng 2NM GAA na sertipikasyon ng Samsung.

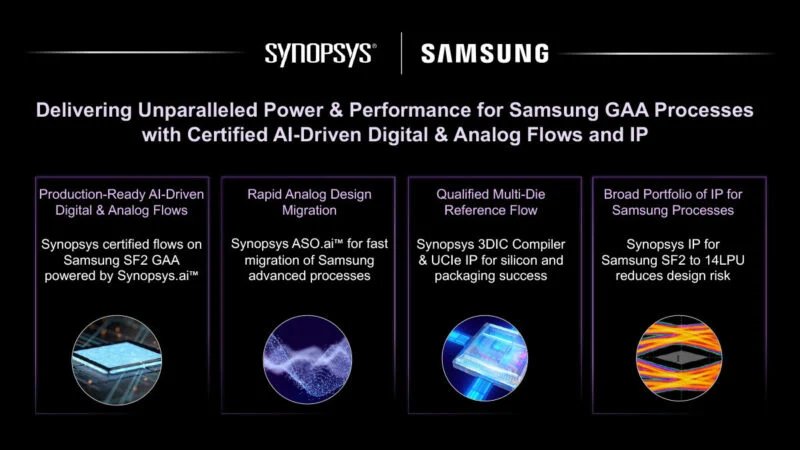

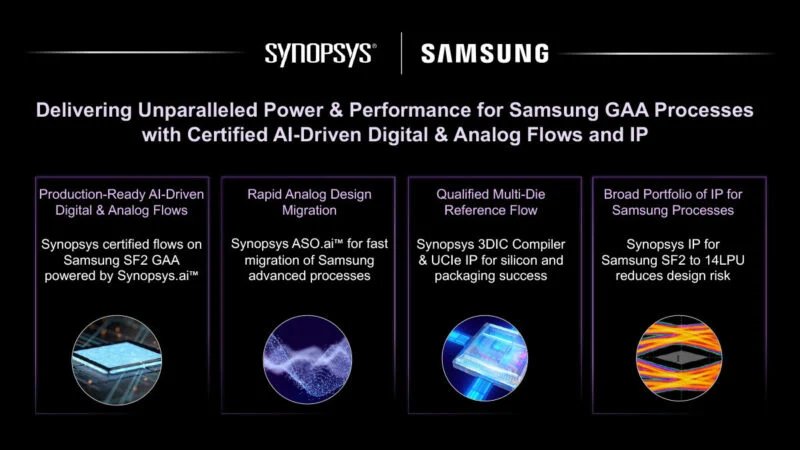

Ayon sa opisyal na pagpapakilala, ang Synopsys 'EDA kit ay maaaring mapabuti ang paglilipat ng disenyo ng simulation, PPA (kahusayan ng lugar, pagganap, at kahusayan ng enerhiya), at pagiging produktibo ng Samsung Wafer Foundry 2NM GAA na proseso ng node.Ginagamit ng Sinopsys ang Artipisyal na Intelligence (AI) para sa pakikipagtulungan sa pag -optimize upang matulungan ang Samsung na mapabuti ang kahusayan ng lugar, pagganap, at kahusayan ng enerhiya ng proseso ng 2nm.

Ang mga tool ng Synopsys 'DSO.AI at ASO.AI ay matagumpay na lumipat mula sa FinFET hanggang sa arkitektura ng GAA, na nangangahulugang ang mga customer ay maaaring maayos na lumipat ng kanilang umiiral na disenyo ng FinFET chip sa bagong proseso ng 2NM GAA.

Ang mga kumpanya ng CHIP ay maaaring gumamit ng mga tool ng Synopsysys upang makabuo ng mga bagong teknolohiya ng disenyo ng chip, kabilang ang mga kable ng suplay ng kuryente sa likuran, mga lokal na pamamaraan ng pang -unawa sa layout, at disenyo ng yunit ng nanosheet, sa gayon ay pagpapabuti ng kahusayan at pagganap ng mga proseso ng SF2.Sinabi ng Samsung na ang proseso ng SF2Z ay maaaring mapabuti ang pagganap, pagkonsumo ng kuryente, at density (sa pamamagitan ng 20%).

Inihayag din ng Synopsys na ang UCIE IP nito ay ginamit sa paggawa ng mga chips sa Samsung SF2 at SF4X na proseso ng node.Bilang karagdagan, ang parehong solusyon sa DTCO ay gagamitin din upang mai -optimize ang proseso ng 1.4nm na proseso ng Samsung (SF1.4).